# Small-signal distributed FET modeling through electromagnetic analysis of the extrinsic structure

<sup>1</sup>A. Cidronali, <sup>1</sup>G. Collodi, <sup>2</sup>A. Santarelli, <sup>2</sup>G. Vannini, <sup>1</sup>G. Manes

<sup>1</sup>Department of Electronics Engineering, University of Florence - Italy

<sup>2</sup>Department of Electronics, Computer Science and Systems, University of Bologna and CNR-CSITE, Research Center of the National Research Council, Bologna - Italy

## Abstract

The paper presents a new approach to the distributed modeling of high frequency transistors suitable for CAD applications. In particular, electromagnetic simulation is adopted to characterize the extrinsic part of the electron device in terms of a multi-port scattering matrix without introducing approximations based on lumped components. Experimental and simulation results for  $0.5\mu\text{m}$  GaAs MESFETs with different gate widths preliminary confirm the consistency of the proposed approach.

## Introduction

The growing number of high frequency MMIC applications is stimulating a considerable effort in electron device modeling. Increasing the operating frequencies makes the transistor sizes, in particular the gate width, more and more comparable with the wavelength. In this case, propagation phenomena along the metalization structure may influence the electrical performance significantly. In order to take into account these effects, the inherent distributed nature of electron devices must be investigated and introduced in the modeling techniques. Many authors have dealt with FET distributed modeling by means of a numeric solution of both the electromagnetic and electron transport problems in a consistent way [1,2]. Although potentially accurate, this approach is not suitable for MMIC CAD due to the very large computing effort required. Other authors have developed MMIC CAD-oriented models [3,4] by considering a cascade of elementary devices, representing the active area, fed by lumped passive networks which should model signal

propagation along the metalizations, terminal coupling, dispersion phenomena as well as any other effect related to the passive structure. Since the accuracy of a lumped approximation of intrinsically distributed phenomena is questionable (especially at very high operating frequencies and for complex device structures) a more natural way of approaching the problem could be based on electromagnetic (EM) simulation of the passive structure [5]. EM simulators are now reaching a relevant level of maturity and enable complex electromagnetic phenomena to be taken into account.

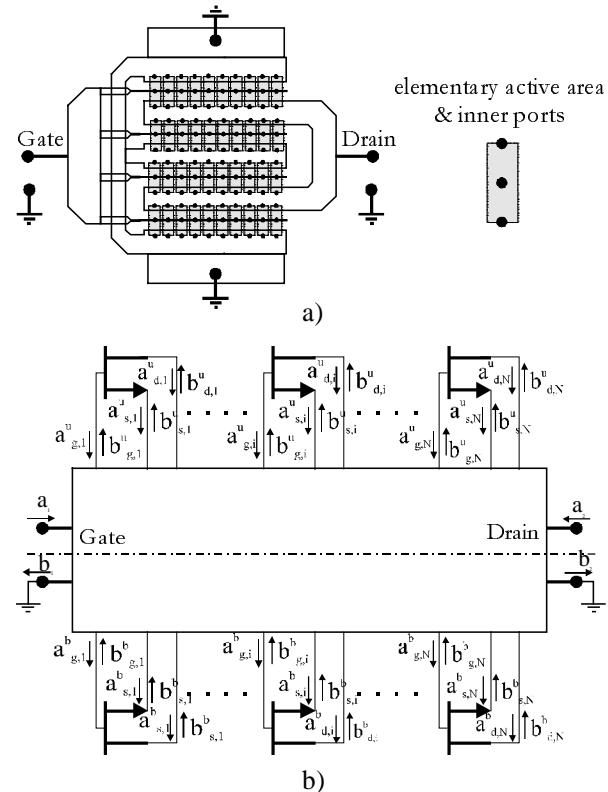

**Fig.1:** FET partitioning: a) structure layout with elementary active area and inner ports; b) schematic representation.

The paper presents a new approach to the distributed modeling of high frequency transistors suitable for MMIC CAD applications. The model consists of two main blocks. The first one considers only the passive part of the transistor, namely the extrinsic structure, while the second one considers the active region, which is sliced in a convenient number of equal elementary devices. The extrinsic part of the electron device is characterized, in terms of scattering parameters, by means of an electromagnetic simulator. This kind of analysis enables the actual device geometry, material stratification as well as losses in the dielectric and metalizations to be taken into account by means of a multi-port S-matrix description for any given device structure and size. Finally, on the basis of measured S-parameters of the electron device, a characterization of the intrinsic active part can be obtained which is consistent with linear scaling rules simply based on the gate width.

### The distributed model structure

The electron device is assumed to consist of a passive network connected with a number of elementary active devices as shown in Fig.1b. This description is intuitively suggested by the structure layout of a conventional FET shown in Fig.1a with the internal interconnections to the elementary devices.

In the first step of the proposed modeling approach the passive structure is characterized, on the basis of layout geometry and material parameters, through its scattering matrix  $\mathbf{S}$  computed by means of electromagnetic simulation.

The subsequent identification of the active region is based on the following considerations: 1) The FET structure presents a longitudinal symmetry axis which is shown in Fig.1; this is practically true for all high frequency transistors. 2) Since the electromagnetic propagation and coupling effects are accounted for by the passive structure, all the elementary devices are

characterized by the same three-port scattering matrix  $\underline{\underline{\beta}}$ . On this basis, it is possible to extract the matrix  $\underline{\underline{\beta}}$  of the active slices once the scattering matrix  $\underline{\underline{\alpha}}$  of the whole electron device has been measured and the matrix  $\mathbf{S}$  of the passive structure computed through EM simulation.

If  $2N$  is the total number of elementary devices adopted in the distributed model, taking into account the symmetric structure shown in Fig.1b, we can write:

$$\begin{aligned}\vec{a}_i &= \vec{a}_i^u = \begin{bmatrix} a_{g,i}^u & a_{d,i}^u & a_{s,i}^u \end{bmatrix} = \vec{a}_i^b = \begin{bmatrix} a_{g,i}^b & a_{d,i}^b & a_{s,i}^b \end{bmatrix} \\ \vec{b}_i &= \vec{b}_i^u = \begin{bmatrix} b_{g,i}^u & b_{d,i}^u & b_{s,i}^u \end{bmatrix} = \vec{b}_i^b = \begin{bmatrix} b_{g,i}^b & b_{d,i}^b & b_{s,i}^b \end{bmatrix}\end{aligned}\quad (1)$$

where: the index  $i$ , ranges from 1 to  $N$ ,  $a_i$  and  $b_i$  are the vectors of the incident and reflected waves at the ports of the  $i$ -th elementary device and  $g$ ,  $d$ ,  $s$  denote the gate, drain and source terminals, respectively.

By using eqns.(1), the linearly dependent rows in the scattering matrix  $\mathbf{S}$  of the passive structure can be eliminated in order to obtain the scattering matrix  $\tilde{\mathbf{S}}$ . Moreover it is possible to demonstrate that:

$$\begin{bmatrix} \vec{b}_1 \\ \vdots \\ \vec{b}_N \end{bmatrix} = \tilde{\mathbf{S}} \cdot \begin{bmatrix} (\underline{\underline{\alpha}} - \underline{\underline{\partial}})^{-1} \cdot \underline{\underline{\gamma}} \\ \underline{\underline{I}} \end{bmatrix} \cdot \begin{bmatrix} \vec{a}_1 \\ \vdots \\ \vec{a}_N \end{bmatrix} \quad (2)$$

where:  $\underline{\underline{\alpha}}$  is the measured scattering matrix of the electron device;  $\underline{\underline{\partial}}$  and  $\underline{\underline{\gamma}}$  are obtained suppressing proper rows and columns in  $\tilde{\mathbf{S}}$  while  $\underline{\underline{I}}$  is the identity matrix.

The matrix  $\underline{\underline{\beta}}$  associated with each elementary device is defined by:

$$\vec{a}_i = \underline{\underline{\beta}} \cdot \vec{b}_i \quad i=1, \dots, N \quad (3)$$

which substituted in (2) leads to a homogenous system of equations from which  $\underline{\underline{\beta}}$  can be computed.

### Model validation

In order to validate the proposed modeling approach two different MESFET structures, FET1 and FET2 biased at  $V_{gs}=0V$  and  $V_{ds}=3V$ , have been considered. The transistors have two gate fingers while the total gate widths are  $2 \times 50\mu\text{m}$  for FET1 and  $2 \times 150\mu\text{m}$  for FET2. A part from their size, the transistors are identical and contained in the same wafer die. On-wafer S-parameter measurements were carried out up to 50 GHz.

For both the test structures the S matrix of the extrinsic part, which accounts for electromagnetic phenomena, was computed by using the commercial EM-Sonnet simulator on the basis of geometry and material parameters provided by the foundry,. To this purpose a convenient number of ports (see Fig.1), which behave as the internal terminals, have been introduced. In particular, EM simulations of the layout of FET1 were carried out both considering one and two active slices per finger and the associated three port scattering matrices  $\underline{\underline{\beta}}_1$  and  $\underline{\underline{\beta}}_2$  were computed, from the knowledge of measured S-parameters, by using the procedure outlined above. More precisely, the matrix  $\underline{\underline{\beta}}_1$  describes a slice of active device corresponding to a width of  $50\mu\text{m}$ , while  $\underline{\underline{\beta}}_2$  corresponds to  $25\mu\text{m}$ .

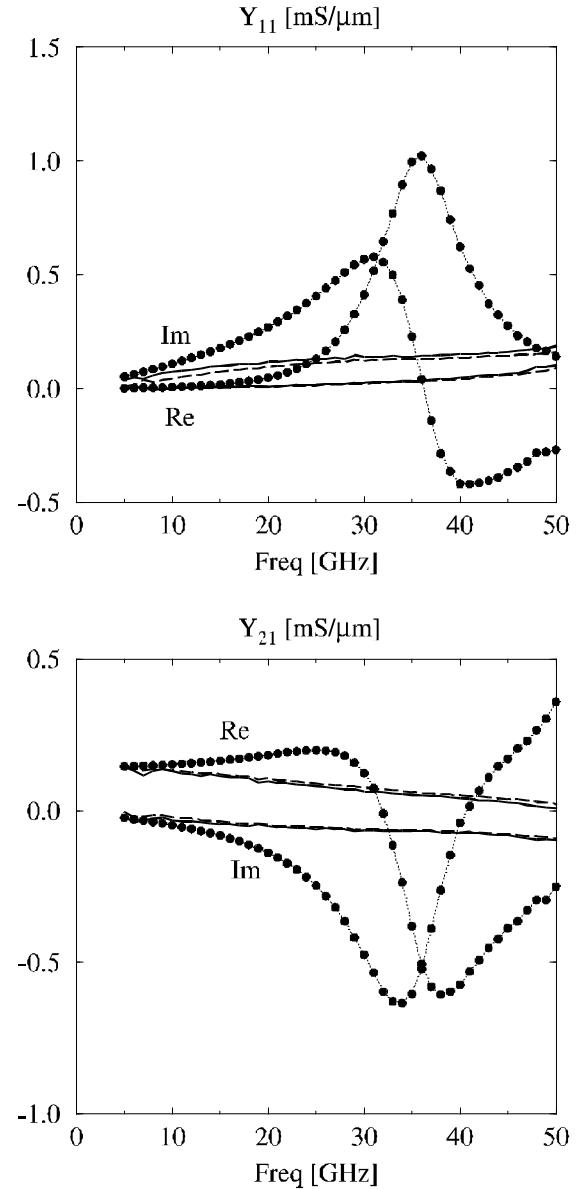

In Figs. 2 and 3, real and imaginary parts of the intrinsic parameters  $Y_{11}$  and  $Y_{21}$  (normalized to the gate width) corresponding to the  $\underline{\underline{\beta}}_1$  and  $\underline{\underline{\beta}}_2$  matrices of the two experiments are plotted as a function of frequency. It is worth noting that these intrinsic parameters show fairly monotonic slopes without the resonant-like behavior typically found in device measurements (see Figs. 2, 3) due to the interaction between device capacitances and inductive/propagation effects

associated to the metalizations. Moreover, the good agreement of the unit-width admittances obtained from  $\underline{\underline{\beta}}_1$  and  $\underline{\underline{\beta}}_2$  seems to suggest that, for a  $50\mu\text{m}$  finger, a number of one/two active slices is sufficient to characterize distributed and propagation phenomena.

**Fig.2, 3:** Real and imaginary parts of the intrinsic  $Y_{11}$  and  $Y_{21}$  per gate unit-width associated to a  $2 \times 50\mu\text{m}$  GaAs MESFET. The agreement between results obtained using one (---) and two (- - -) active slices per finger is good. The intrinsic parameters do not show the resonant-like behavior typically found in device measurements (●)

(drawn normalized to the gate width for an easier comparison).

Thanks to the EM modeling of propagation effects, the admittance matrix per gate unit-width of the active area can be determined and potentially adopted to predict the behavior of any transistor structure, once the extrinsic region of the device has been characterized through EM simulation.

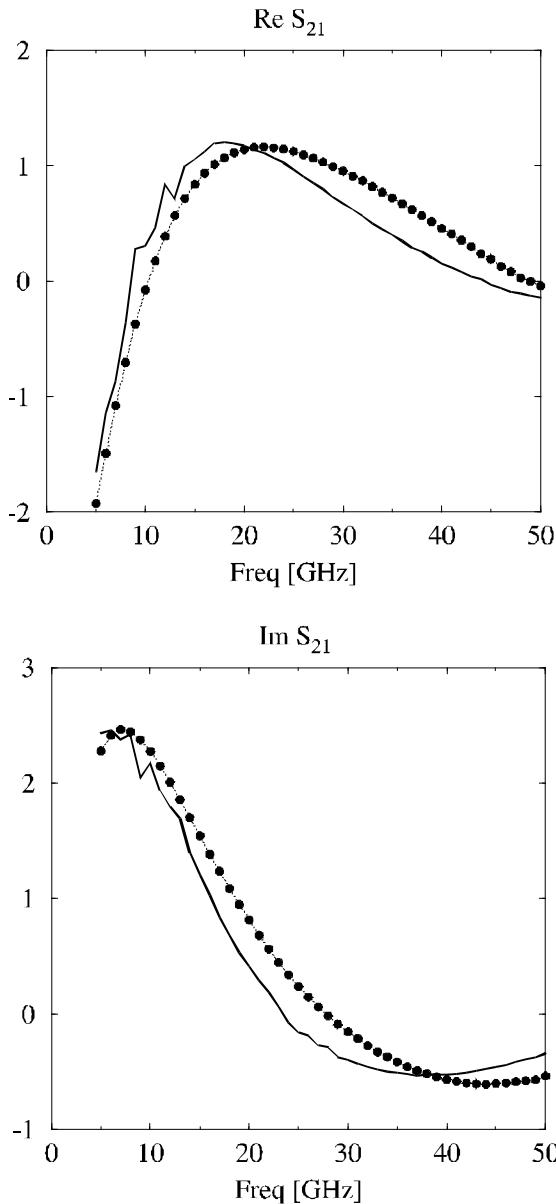

**Fig.4, 5:** Real and imaginary part of S<sub>21</sub> for the 2x150μm GaAs MESFET. The prediction (---) computed on the basis of the unit-width admittance matrix obtained

from a 2x50μm device is in good agreement with measurements (•).

To test this issue, the admittance matrix obtained from the  $\beta_2$  matrix (corresponding to 25μm) of the elementary device extracted from FET1 (2x50μm) has been adopted to predict the behavior of FET2 (2x150μm). More precisely, six  $\beta_2$  slices per finger have been used in conjunction with a consistent S-matrix of the FET2 passive structure computed through EM simulation. The comparison between measured and predicted S<sub>21</sub>, plotted in Fig.4 and 5, shows a reasonably good agreement which gives a positive indication of the potentiality of this approach.

## References.

- [1] M.A.Alsunaidi, S.M. Imtiaz, S. M. El-Ghazaly, "Electromagnetic wave effects on microwave transistor using a full-wave time-domain model," *IEEE Trans. Microwave Theory Tech.*, Vol.44, no. 6, June 1996, pp. 799-808.

- [2] A.Cidronali, G. Collodi, G. Leuzzi, G. Manes, "Numerical analysis of a 0.2 μm AlGaAs|GaAs HEMT including electromagnetic effects," *IEEE International Symposium on Compound Semiconductor*, San Diego (CA), 7-11 September 1997.

- [3] K. Hajji, F. M. Ghannouchi, "Small-signal distributed model for GaAs HBT'S and S-parameter prediction at millimeter-wave frequencies" *IEEE Trans. Microwave Theory Tech.*, Vol.44, no. 5, January 1997, pp. 723-732.

- [4] B.Castillo-Vazquez, T.M. Martin-Guerrero, C. Camacho-Penalosa "Scaleable distributed model for microwave and millimeter-wave monolithic FET type devices" 5<sup>th</sup> European Gallium Arsenide and related III-V compounds application symposium Bologna Italy Sept. 3-5 1997

- [5] G.Avitabile, A.Cidronali, G.Vannini, G.Manes, "Multifinger effects in a GaAs FET distributed large signal CAD model", *Proc. of the 1996 IEEE IEDM*, International Electron Device Meeting, San Francisco, USA, December 1996.